|

CMSIS2000

0.0.7

|

|

CMSIS2000

0.0.7

|

|

Data Structures | |

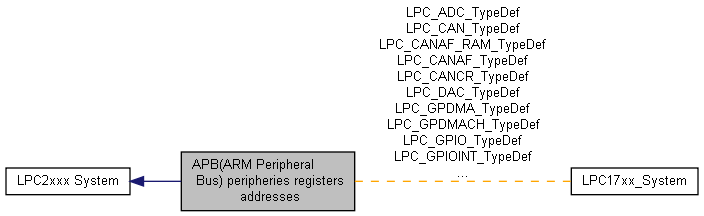

| struct | LPC_ADC_TypeDef |

| Analog-to-Digital Converter (ADC) register structure definition. More... | |

| struct | LPC_CAN_TypeDef |

| Controller Area Network Controller (CAN) register structure definition. More... | |

| struct | LPC_CANAF_RAM_TypeDef |

| Controller Area Network Acceptance Filter RAM (CANAF_RAM)structure definition. More... | |

| struct | LPC_CANAF_TypeDef |

| Controller Area Network Acceptance Filter(CANAF) register structure definition. More... | |

| struct | LPC_CANCR_TypeDef |

| Controller Area Network Central (CANCR) register structure definition. More... | |

| struct | LPC_DAC_TypeDef |

| Digital-to-Analog Converter (DAC) register structure definition. More... | |

| struct | LPC_GPDMA_TypeDef |

| General Purpose Direct Memory Access (GPDMA) register structure definition. More... | |

| struct | LPC_GPDMACH_TypeDef |

| General Purpose Direct Memory Access Channel (GPDMACH) register structure definition. More... | |

| struct | LPC_GPIO_TypeDef |

| General Purpose Input/Output (GPIO) register structure definition. More... | |

| struct | LPC_GPIOINT_TypeDef |

| General Purpose Input/Output interrupt (GPIOINT) register structure definition. More... | |

| struct | LPC_I2C_TypeDef |

| Inter-Integrated Circuit (I2C) register structure definition. More... | |

| struct | LPC_I2S_TypeDef |

| Inter IC Sound (I2S) register structure definition. More... | |

| struct | LPC_IO_TypeDef_old |

| General Purpose Input/Output (GPIO) register structure definition old pins style control. More... | |

| struct | LPC_MCI_TypeDef |

| MultiMedia Card Interface(MCI) Controller register structure definition. More... | |

| struct | LPC_PINCON_TypeDef |

| Pin Connect Block (PINCON) register structure definition. More... | |

| struct | LPC_PWM_TypeDef |

| Pulse-Width Modulation (PWM) register structure definition. More... | |

| struct | LPC_RTC_TypeDef |

| Real-Time Clock (RTC) register structure definition. More... | |

| struct | LPC_SC_TypeDef |

| System Control (SC) register structure definition. More... | |

| struct | LPC_SPI_TypeDef |

| Serial Peripheral Interface (SPI) register structure definition. More... | |

| struct | LPC_SSP_TypeDef |

| Synchronous Serial Communication (SSP) register structure definition. More... | |

| struct | LPC_TIM_TypeDef |

| Timer (TIM) register structure definition. More... | |

| struct | LPC_UART1_TypeDef |

| Universal Asynchronous Receiver Transmitter 1 (UART1) register structure definition. More... | |

| struct | LPC_UART_TypeDef |

| Universal Asynchronous Receiver Transmitter (UART) register structure definition. More... | |

| struct | LPC_USB_TypeDef |

| Universal Serial Bus (USB) register structure definition. More... | |

| struct | LPC_WDT_TypeDef |

| Watchdog Timer (WDT) register structure definition. More... | |

| struct | VIC_TypeDef |

| #define LPC_ADC ((LPC_ADC_TypeDef *) LPC_AD0_BASE ) |

| #define LPC_CAN1 ((LPC_CAN_TypeDef *) LPC_CAN1_BASE ) |

| #define LPC_CAN2 ((LPC_CAN_TypeDef *) LPC_CAN2_BASE ) |

| #define LPC_CANAF ((LPC_CANAF_TypeDef *) LPC_CANAF_BASE ) |

| #define LPC_CANAF_RAM ((LPC_CANAF_RAM_TypeDef *) LPC_CANAF_RAM_BASE) |

| #define LPC_CANCR ((LPC_CANCR_TypeDef *) LPC_CANCR_BASE ) |

| #define LPC_DAC ((LPC_DAC_TypeDef *) LPC_DAC_BASE ) |

| #define LPC_GPIO0 ((LPC_GPIO_TypeDef *) LPC_GPIO0_BASE ) |

| #define LPC_GPIO1 ((LPC_GPIO_TypeDef *) LPC_GPIO1_BASE ) |

| #define LPC_GPIO2 ((LPC_GPIO_TypeDef *) LPC_GPIO2_BASE ) |

| #define LPC_GPIO3 ((LPC_GPIO_TypeDef *) LPC_GPIO3_BASE ) |

| #define LPC_GPIO4 ((LPC_GPIO_TypeDef *) LPC_GPIO4_BASE ) |

| #define LPC_GPIOINT ((LPC_GPIOINT_TypeDef *) LPC_GPIOINT_BASE ) |

| #define LPC_I2C0 ((LPC_I2C_TypeDef *) LPC_I2C0_BASE ) |

| #define LPC_I2C1 ((LPC_I2C_TypeDef *) LPC_I2C1_BASE ) |

| #define LPC_I2C2 ((LPC_I2C_TypeDef *) LPC_I2C2_BASE ) |

| #define LPC_IO ((LPC_IO_TypeDef_old *) LPC_GPIO_BASE ) |

| #define LPC_IO0 ((LPC_IO_TypeDef_old *) LPC_GPIO_BASE ) |

| #define LPC_IO1 ((LPC_IO_TypeDef_old *) LPC_GPIO_BASE + 0x10) |

| #define LPC_MCPWM ((LPC_MCPWM_TypeDef *) LPC_MCPWM_BASE ) |

| #define LPC_PINCON ((LPC_PINCON_TypeDef *) LPC_PINSEL_BASE ) |

| #define LPC_PWM0 ((LPC_PWM_TypeDef *) LPC_PWM0_BASE ) |

| #define LPC_PWM1 ((LPC_PWM_TypeDef *) LPC_PWM1_BASE ) |

| #define LPC_QEI ((LPC_QEI_TypeDef *) LPC_QEI_BASE ) |

| #define LPC_RIT ((LPC_RIT_TypeDef *) LPC_RIT_BASE ) |

| #define LPC_RTC ((LPC_RTC_TypeDef *) LPC_RTC_BASE ) |

| #define LPC_SC ((LPC_SC_TypeDef *) LPC_SC_BASE ) |

| #define LPC_SC_PLLSTAT_PLLC_Pos (LPC_SC_PLLSTAT_PLLE_Pos + 1) |

| #define LPC_SC_PLLSTAT_PLLE_Pos 8 |

| #define LPC_SC_PLLSTAT_PLOCK_Pos (LPC_SC_PLLSTAT_PLLE_Pos + 2) |

| #define LPC_SPI ((LPC_SPI_TypeDef *) LPC_SPI_BASE ) |

| #define LPC_SSP0 ((LPC_SSP_TypeDef *) LPC_SSP0_BASE ) |

| #define LPC_SSP1 ((LPC_SSP_TypeDef *) LPC_SSP1_BASE ) |

| #define LPC_TIM0 ((LPC_TIM_TypeDef *) LPC_TIM0_BASE ) |

| #define LPC_TIM1 ((LPC_TIM_TypeDef *) LPC_TIM1_BASE ) |

| #define LPC_TIM2 ((LPC_TIM_TypeDef *) LPC_TIM2_BASE ) |

| #define LPC_TIM3 ((LPC_TIM_TypeDef *) LPC_TIM3_BASE ) |

| #define LPC_UART0 ((LPC_UART_TypeDef *) LPC_UART0_BASE ) |

| #define LPC_UART1 ((LPC_UART1_TypeDef *) LPC_UART1_BASE ) |

| #define LPC_UART2 ((LPC_UART_TypeDef *) LPC_UART2_BASE ) |

| #define LPC_UART3 ((LPC_UART_TypeDef *) LPC_UART3_BASE ) |

| #define LPC_WDT ((LPC_WDT_TypeDef *) LPC_WDT_BASE ) |

| #define PLLCFG_Val (PLL_MValue | (PLL_NValue << 5)) |

| #define VIC ((VIC_TypeDef *) VIC_BASE ) |

Definition at line 1721 of file LPC2xxx.h.

Referenced by NVIC_DisableIRQ(), NVIC_EnableIRQ(), NVIC_SetPriority(), SystemVIC_Init(), and SystemVIC_SetISR().

| #define VIC_MAX_IRQ_NUMBER (VIC_SIZE-1) |

Definition at line 182 of file LPC2xxx.h.

Referenced by SystemVIC_Init(), and SystemVIC_SetISR().

| #define VIC_SIZE 16 |

Definition at line 148 of file LPC2xxx.h.

Referenced by SystemVIC_SetISR().