|

CMSIS2000

0.0.7

|

|

CMSIS2000

0.0.7

|

|

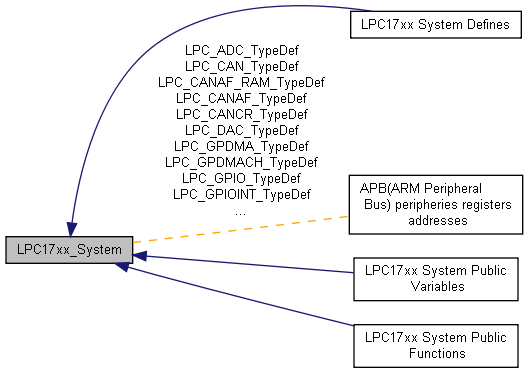

Modules | |

| LPC17xx System Defines | |

| LPC17xx System Public Variables | |

| LPC17xx System Public Functions | |

Data Structures | |

| struct | LPC_ADC_TypeDef |

| Analog-to-Digital Converter (ADC) register structure definition. More... | |

| struct | LPC_CAN_TypeDef |

| Controller Area Network Controller (CAN) register structure definition. More... | |

| struct | LPC_CANAF_RAM_TypeDef |

| Controller Area Network Acceptance Filter RAM (CANAF_RAM)structure definition. More... | |

| struct | LPC_CANAF_TypeDef |

| Controller Area Network Acceptance Filter(CANAF) register structure definition. More... | |

| struct | LPC_CANCR_TypeDef |

| Controller Area Network Central (CANCR) register structure definition. More... | |

| struct | LPC_DAC_TypeDef |

| Digital-to-Analog Converter (DAC) register structure definition. More... | |

| struct | LPC_EMAC_TypeDef |

| Ethernet Media Access Controller (EMAC) register structure definition. More... | |

| struct | LPC_GPDMA_TypeDef |

| General Purpose Direct Memory Access (GPDMA) register structure definition. More... | |

| struct | LPC_GPDMACH_TypeDef |

| General Purpose Direct Memory Access Channel (GPDMACH) register structure definition. More... | |

| struct | LPC_GPIO_TypeDef |

| General Purpose Input/Output (GPIO) register structure definition. More... | |

| struct | LPC_GPIOINT_TypeDef |

| General Purpose Input/Output interrupt (GPIOINT) register structure definition. More... | |

| struct | LPC_I2C_TypeDef |

| Inter-Integrated Circuit (I2C) register structure definition. More... | |

| struct | LPC_I2S_TypeDef |

| Inter IC Sound (I2S) register structure definition. More... | |

| struct | LPC_MCPWM_TypeDef |

| Motor Control Pulse-Width Modulation (MCPWM) register structure definition. More... | |

| struct | LPC_PINCON_TypeDef |

| Pin Connect Block (PINCON) register structure definition. More... | |

| struct | LPC_PWM_TypeDef |

| Pulse-Width Modulation (PWM) register structure definition. More... | |

| struct | LPC_QEI_TypeDef |

| Quadrature Encoder Interface (QEI) register structure definition. More... | |

| struct | LPC_RIT_TypeDef |

| Repetitive Interrupt Timer (RIT) register structure definition. More... | |

| struct | LPC_RTC_TypeDef |

| Real-Time Clock (RTC) register structure definition. More... | |

| struct | LPC_SC_TypeDef |

| System Control (SC) register structure definition. More... | |

| struct | LPC_SPI_TypeDef |

| Serial Peripheral Interface (SPI) register structure definition. More... | |

| struct | LPC_SSP_TypeDef |

| Synchronous Serial Communication (SSP) register structure definition. More... | |

| struct | LPC_TIM_TypeDef |

| Timer (TIM) register structure definition. More... | |

| struct | LPC_UART0_TypeDef |

| Universal Asynchronous Receiver Transmitter 0 (UART0) register structure definition. More... | |

| struct | LPC_UART1_TypeDef |

| Universal Asynchronous Receiver Transmitter 1 (UART1) register structure definition. More... | |

| struct | LPC_UART_TypeDef |

| Universal Asynchronous Receiver Transmitter (UART) register structure definition. More... | |

| struct | LPC_USB_TypeDef |

| Universal Serial Bus (USB) register structure definition. More... | |

| struct | LPC_WDT_TypeDef |

| Watchdog Timer (WDT) register structure definition. More... | |

Typedefs | |

| typedef enum IRQn | IRQn_Type |

| IRQ interrupt source definition. | |

Functions | |

| void | SystemCoreClockUpdate (void) |

| Update SystemCoreClock variable. | |

| void | SystemInit (void) |

| Initialize the system. | |

Variables | |

| uint32_t | SystemCoreClock |

| #define __NVIC_PRIO_BITS 5 |

| #define __Vendor_SysTickConfig 0 |

| #define IRC_OSC ( 4000000UL) /* Internal RC oscillator frequency */ |

Definition at line 85 of file system_LPC17xx.h.

| #define LPC_ADC ((LPC_ADC_TypeDef *) LPC_ADC_BASE ) |

| #define LPC_ADC_BASE (LPC_APB0_BASE + 0x34000) |

| #define LPC_CAN1 ((LPC_CAN_TypeDef *) LPC_CAN1_BASE ) |

| #define LPC_CAN1_BASE (LPC_APB0_BASE + 0x44000) |

| #define LPC_CAN2 ((LPC_CAN_TypeDef *) LPC_CAN2_BASE ) |

| #define LPC_CAN2_BASE (LPC_APB0_BASE + 0x48000) |

| #define LPC_CANAF ((LPC_CANAF_TypeDef *) LPC_CANAF_BASE ) |

| #define LPC_CANAF_BASE (LPC_APB0_BASE + 0x3C000) |

| #define LPC_CANAF_RAM ((LPC_CANAF_RAM_TypeDef *) LPC_CANAF_RAM_BASE) |

| #define LPC_CANAF_RAM_BASE (LPC_APB0_BASE + 0x38000) |

| #define LPC_CANCR ((LPC_CANCR_TypeDef *) LPC_CANCR_BASE ) |

| #define LPC_CANCR_BASE (LPC_APB0_BASE + 0x40000) |

| #define LPC_DAC ((LPC_DAC_TypeDef *) LPC_DAC_BASE ) |

| #define LPC_DAC_BASE (LPC_APB1_BASE + 0x0C000) |

| #define LPC_EMAC ((LPC_EMAC_TypeDef *) LPC_EMAC_BASE ) |

| #define LPC_EMAC_BASE (LPC_AHB_BASE + 0x00000) |

| #define LPC_GPDMA ((LPC_GPDMA_TypeDef *) LPC_GPDMA_BASE ) |

| #define LPC_GPDMA_BASE (LPC_AHB_BASE + 0x04000) |

| #define LPC_GPDMACH0 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH0_BASE ) |

| #define LPC_GPDMACH0_BASE (LPC_AHB_BASE + 0x04100) |

| #define LPC_GPDMACH1 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH1_BASE ) |

| #define LPC_GPDMACH1_BASE (LPC_AHB_BASE + 0x04120) |

| #define LPC_GPDMACH2 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH2_BASE ) |

| #define LPC_GPDMACH2_BASE (LPC_AHB_BASE + 0x04140) |

| #define LPC_GPDMACH3 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH3_BASE ) |

| #define LPC_GPDMACH3_BASE (LPC_AHB_BASE + 0x04160) |

| #define LPC_GPDMACH4 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH4_BASE ) |

| #define LPC_GPDMACH4_BASE (LPC_AHB_BASE + 0x04180) |

| #define LPC_GPDMACH5 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH5_BASE ) |

| #define LPC_GPDMACH5_BASE (LPC_AHB_BASE + 0x041A0) |

| #define LPC_GPDMACH6 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH6_BASE ) |

| #define LPC_GPDMACH6_BASE (LPC_AHB_BASE + 0x041C0) |

| #define LPC_GPDMACH7 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH7_BASE ) |

| #define LPC_GPDMACH7_BASE (LPC_AHB_BASE + 0x041E0) |

| #define LPC_GPIO0 ((LPC_GPIO_TypeDef *) LPC_GPIO0_BASE ) |

| #define LPC_GPIO0_BASE (LPC_GPIO_BASE + 0x00000) |

| #define LPC_GPIO1 ((LPC_GPIO_TypeDef *) LPC_GPIO1_BASE ) |

| #define LPC_GPIO1_BASE (LPC_GPIO_BASE + 0x00020) |

| #define LPC_GPIO2 ((LPC_GPIO_TypeDef *) LPC_GPIO2_BASE ) |

| #define LPC_GPIO2_BASE (LPC_GPIO_BASE + 0x00040) |

| #define LPC_GPIO3 ((LPC_GPIO_TypeDef *) LPC_GPIO3_BASE ) |

| #define LPC_GPIO3_BASE (LPC_GPIO_BASE + 0x00060) |

| #define LPC_GPIO4 ((LPC_GPIO_TypeDef *) LPC_GPIO4_BASE ) |

| #define LPC_GPIO4_BASE (LPC_GPIO_BASE + 0x00080) |

| #define LPC_GPIOINT ((LPC_GPIOINT_TypeDef *) LPC_GPIOINT_BASE ) |

| #define LPC_GPIOINT_BASE (LPC_APB0_BASE + 0x28080) |

| #define LPC_I2C0 ((LPC_I2C_TypeDef *) LPC_I2C0_BASE ) |

| #define LPC_I2C0_BASE (LPC_APB0_BASE + 0x1C000) |

| #define LPC_I2C1 ((LPC_I2C_TypeDef *) LPC_I2C1_BASE ) |

| #define LPC_I2C1_BASE (LPC_APB0_BASE + 0x5C000) |

| #define LPC_I2C2 ((LPC_I2C_TypeDef *) LPC_I2C2_BASE ) |

| #define LPC_I2C2_BASE (LPC_APB1_BASE + 0x20000) |

| #define LPC_I2S ((LPC_I2S_TypeDef *) LPC_I2S_BASE ) |

| #define LPC_I2S_BASE (LPC_APB1_BASE + 0x28000) |

| #define LPC_MCPWM ((LPC_MCPWM_TypeDef *) LPC_MCPWM_BASE ) |

| #define LPC_MCPWM_BASE (LPC_APB1_BASE + 0x38000) |

| #define LPC_PINCON ((LPC_PINCON_TypeDef *) LPC_PINCON_BASE ) |

| #define LPC_PINCON_BASE (LPC_APB0_BASE + 0x2C000) |

| #define LPC_PWM1 ((LPC_PWM_TypeDef *) LPC_PWM1_BASE ) |

| #define LPC_PWM1_BASE (LPC_APB0_BASE + 0x18000) |

| #define LPC_QEI ((LPC_QEI_TypeDef *) LPC_QEI_BASE ) |

| #define LPC_QEI_BASE (LPC_APB1_BASE + 0x3C000) |

| #define LPC_RIT ((LPC_RIT_TypeDef *) LPC_RIT_BASE ) |

| #define LPC_RIT_BASE (LPC_APB1_BASE + 0x30000) |

| #define LPC_RTC ((LPC_RTC_TypeDef *) LPC_RTC_BASE ) |

| #define LPC_RTC_BASE (LPC_APB0_BASE + 0x24000) |

| #define LPC_SC ((LPC_SC_TypeDef *) LPC_SC_BASE ) |

Definition at line 1088 of file LPC17xx.h.

Referenced by SystemCoreClockUpdate(), and SystemInit().

| #define LPC_SC_BASE (LPC_APB1_BASE + 0x7C000) |

| #define LPC_SPI ((LPC_SPI_TypeDef *) LPC_SPI_BASE ) |

| #define LPC_SPI_BASE (LPC_APB0_BASE + 0x20000) |

| #define LPC_SSP0 ((LPC_SSP_TypeDef *) LPC_SSP0_BASE ) |

| #define LPC_SSP0_BASE (LPC_APB1_BASE + 0x08000) |

| #define LPC_SSP1 ((LPC_SSP_TypeDef *) LPC_SSP1_BASE ) |

| #define LPC_SSP1_BASE (LPC_APB0_BASE + 0x30000) |

| #define LPC_TIM0 ((LPC_TIM_TypeDef *) LPC_TIM0_BASE ) |

| #define LPC_TIM0_BASE (LPC_APB0_BASE + 0x04000) |

| #define LPC_TIM1 ((LPC_TIM_TypeDef *) LPC_TIM1_BASE ) |

| #define LPC_TIM1_BASE (LPC_APB0_BASE + 0x08000) |

| #define LPC_TIM2 ((LPC_TIM_TypeDef *) LPC_TIM2_BASE ) |

| #define LPC_TIM2_BASE (LPC_APB1_BASE + 0x10000) |

| #define LPC_TIM3 ((LPC_TIM_TypeDef *) LPC_TIM3_BASE ) |

| #define LPC_TIM3_BASE (LPC_APB1_BASE + 0x14000) |

| #define LPC_UART0 ((LPC_UART_TypeDef *) LPC_UART0_BASE ) |

| #define LPC_UART0_BASE (LPC_APB0_BASE + 0x0C000) |

| #define LPC_UART1 ((LPC_UART1_TypeDef *) LPC_UART1_BASE ) |

| #define LPC_UART1_BASE (LPC_APB0_BASE + 0x10000) |

| #define LPC_UART2 ((LPC_UART_TypeDef *) LPC_UART2_BASE ) |

| #define LPC_UART2_BASE (LPC_APB1_BASE + 0x18000) |

| #define LPC_UART3 ((LPC_UART_TypeDef *) LPC_UART3_BASE ) |

| #define LPC_UART3_BASE (LPC_APB1_BASE + 0x1C000) |

| #define LPC_USB ((LPC_USB_TypeDef *) LPC_USB_BASE ) |

| #define LPC_USB_BASE (LPC_AHB_BASE + 0x0C000) |

| #define LPC_WDT ((LPC_WDT_TypeDef *) LPC_WDT_BASE ) |

| #define LPC_WDT_BASE (LPC_APB0_BASE + 0x00000) |

| #define OSC_CLK ( XTAL_HZ) /* Main oscillator frequency */ |

Definition at line 79 of file system_LPC17xx.h.

| #define RTC_CLK ( 32768UL) /* RTC oscillator frequency */ |

Definition at line 82 of file system_LPC17xx.h.

| #define WDT_OSC ( 500000UL) /* Internal WDT oscillator frequency */ |

Definition at line 88 of file system_LPC17xx.h.

| #define XTAL_HZ (12000000UL) /* Oscillator frequency */ |

Definition at line 76 of file system_LPC17xx.h.

| enum IRQn |

IRQ interrupt source definition.

| void SystemCoreClockUpdate | ( | void | ) |

Update SystemCoreClock variable.

| none |

Updates the SystemCoreClock with current core Clock retrieved from cpu registers.

Definition at line 45 of file system_ARMCM0.c.

References __SYSTEM_CLOCK, IRC_OSC, LPC_SC, OSC_CLK, RTC_CLK, and SystemCoreClock.

| void SystemInit | ( | void | ) |

Initialize the system.

| none |

Setup the microcontroller system. Initialize the System and update the SystemCoreClock variable.

| none |

Setup the microcontroller system. Initialize the System.

Setup the microcontroller system. Initialize the System and update the SystemCoreClock variable.

Definition at line 61 of file system_ARMCM0.c.

| uint32_t SystemCoreClock |

System Clock Frequency (Core Clock)

Definition at line 39 of file system_ARMCM0.c.