|

CMSIS2000

0.0.7

|

|

CMSIS2000

0.0.7

|

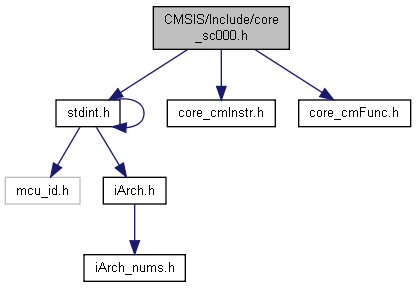

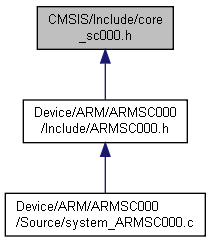

CMSIS SC000 Core Peripheral Access Layer Header File. Подробнее...

Структуры данных | |

| union | APSR_Type |

| Union type to access the Application Program Status Register (APSR). Подробнее... | |

| union | CONTROL_Type |

| Union type to access the Control Registers (CONTROL). Подробнее... | |

| union | IPSR_Type |

| Union type to access the Interrupt Program Status Register (IPSR). Подробнее... | |

| struct | NVIC_Type |

| Structure type to access the Nested Vectored Interrupt Controller (NVIC). Подробнее... | |

| struct | SCB_Type |

| Structure type to access the System Control Block (SCB). Подробнее... | |

| struct | SCnSCB_Type |

| Structure type to access the System Control and ID Register not in the SCB. Подробнее... | |

| struct | SysTick_Type |

| Structure type to access the System Timer (SysTick). Подробнее... | |

| union | xPSR_Type |

| Union type to access the Special-Purpose Program Status Registers (xPSR). Подробнее... | |

Макросы | |

| #define | __CORE_SC000_H_GENERIC |

| #define | _BIT_SHIFT(IRQn) ( (((uint32_t)(IRQn) ) & 0x03) * 8 ) |

| #define | _IP_IDX(IRQn) ( ((uint32_t)(IRQn) >> 2) ) |

| #define | _SHP_IDX(IRQn) ( ((((uint32_t)(IRQn) & 0x0F)-8) >> 2) ) |

| #define | NVIC ((NVIC_Type *) NVIC_BASE ) |

| #define | NVIC_BASE (SCS_BASE + 0x0100UL) |

| #define | SCB ((SCB_Type *) SCB_BASE ) |

| #define | SCB_AIRCR_ENDIANESS_Msk (1UL << SCB_AIRCR_ENDIANESS_Pos) |

| #define | SCB_AIRCR_ENDIANESS_Pos 15 |

| #define | SCB_AIRCR_SYSRESETREQ_Msk (1UL << SCB_AIRCR_SYSRESETREQ_Pos) |

| #define | SCB_AIRCR_SYSRESETREQ_Pos 2 |

| #define | SCB_AIRCR_VECTCLRACTIVE_Msk (1UL << SCB_AIRCR_VECTCLRACTIVE_Pos) |

| #define | SCB_AIRCR_VECTCLRACTIVE_Pos 1 |

| #define | SCB_AIRCR_VECTKEY_Msk (0xFFFFUL << SCB_AIRCR_VECTKEY_Pos) |

| #define | SCB_AIRCR_VECTKEY_Pos 16 |

| #define | SCB_AIRCR_VECTKEYSTAT_Msk (0xFFFFUL << SCB_AIRCR_VECTKEYSTAT_Pos) |

| #define | SCB_AIRCR_VECTKEYSTAT_Pos 16 |

| #define | SCB_BASE (SCS_BASE + 0x0D00UL) |

| #define | SCB_CCR_STKALIGN_Msk (1UL << SCB_CCR_STKALIGN_Pos) |

| #define | SCB_CCR_STKALIGN_Pos 9 |

| #define | SCB_CCR_UNALIGN_TRP_Msk (1UL << SCB_CCR_UNALIGN_TRP_Pos) |

| #define | SCB_CCR_UNALIGN_TRP_Pos 3 |

| #define | SCB_CPUID_ARCHITECTURE_Msk (0xFUL << SCB_CPUID_ARCHITECTURE_Pos) |

| #define | SCB_CPUID_ARCHITECTURE_Pos 16 |

| #define | SCB_CPUID_IMPLEMENTER_Msk (0xFFUL << SCB_CPUID_IMPLEMENTER_Pos) |

| #define | SCB_CPUID_IMPLEMENTER_Pos 24 |

| #define | SCB_CPUID_PARTNO_Msk (0xFFFUL << SCB_CPUID_PARTNO_Pos) |

| #define | SCB_CPUID_PARTNO_Pos 4 |

| #define | SCB_CPUID_REVISION_Msk (0xFUL << SCB_CPUID_REVISION_Pos) |

| #define | SCB_CPUID_REVISION_Pos 0 |

| #define | SCB_CPUID_VARIANT_Msk (0xFUL << SCB_CPUID_VARIANT_Pos) |

| #define | SCB_CPUID_VARIANT_Pos 20 |

| #define | SCB_ICSR_ISRPENDING_Msk (1UL << SCB_ICSR_ISRPENDING_Pos) |

| #define | SCB_ICSR_ISRPENDING_Pos 22 |

| #define | SCB_ICSR_ISRPREEMPT_Msk (1UL << SCB_ICSR_ISRPREEMPT_Pos) |

| #define | SCB_ICSR_ISRPREEMPT_Pos 23 |

| #define | SCB_ICSR_NMIPENDSET_Msk (1UL << SCB_ICSR_NMIPENDSET_Pos) |

| #define | SCB_ICSR_NMIPENDSET_Pos 31 |

| #define | SCB_ICSR_PENDSTCLR_Msk (1UL << SCB_ICSR_PENDSTCLR_Pos) |

| #define | SCB_ICSR_PENDSTCLR_Pos 25 |

| #define | SCB_ICSR_PENDSTSET_Msk (1UL << SCB_ICSR_PENDSTSET_Pos) |

| #define | SCB_ICSR_PENDSTSET_Pos 26 |

| #define | SCB_ICSR_PENDSVCLR_Msk (1UL << SCB_ICSR_PENDSVCLR_Pos) |

| #define | SCB_ICSR_PENDSVCLR_Pos 27 |

| #define | SCB_ICSR_PENDSVSET_Msk (1UL << SCB_ICSR_PENDSVSET_Pos) |

| #define | SCB_ICSR_PENDSVSET_Pos 28 |

| #define | SCB_ICSR_VECTACTIVE_Msk (0x1FFUL << SCB_ICSR_VECTACTIVE_Pos) |

| #define | SCB_ICSR_VECTACTIVE_Pos 0 |

| #define | SCB_ICSR_VECTPENDING_Msk (0x1FFUL << SCB_ICSR_VECTPENDING_Pos) |

| #define | SCB_ICSR_VECTPENDING_Pos 12 |

| #define | SCB_SCR_SEVONPEND_Msk (1UL << SCB_SCR_SEVONPEND_Pos) |

| #define | SCB_SCR_SEVONPEND_Pos 4 |

| #define | SCB_SCR_SLEEPDEEP_Msk (1UL << SCB_SCR_SLEEPDEEP_Pos) |

| #define | SCB_SCR_SLEEPDEEP_Pos 2 |

| #define | SCB_SCR_SLEEPONEXIT_Msk (1UL << SCB_SCR_SLEEPONEXIT_Pos) |

| #define | SCB_SCR_SLEEPONEXIT_Pos 1 |

| #define | SCB_SFCR_SECKEY_Msk (0xFFFFUL << SCB_SHCSR_SVCALLPENDED_Pos) |

| #define | SCB_SFCR_SECKEY_Pos 16 |

| #define | SCB_SFCR_UNIBRTIMING_Msk (1UL << SCB_SHCSR_SVCALLPENDED_Pos) |

| #define | SCB_SFCR_UNIBRTIMING_Pos 0 |

| #define | SCB_SHCSR_SVCALLPENDED_Msk (1UL << SCB_SHCSR_SVCALLPENDED_Pos) |

| #define | SCB_SHCSR_SVCALLPENDED_Pos 15 |

| #define | SCB_VTOR_TBLOFF_Msk (0x1FFFFFFUL << SCB_VTOR_TBLOFF_Pos) |

| #define | SCB_VTOR_TBLOFF_Pos 7 |

| #define | SCnSCB ((SCnSCB_Type *) SCS_BASE ) |

| #define | SCnSCB_ACTLR_DISMCYCINT_Msk (1UL << SCnSCB_ACTLR_DISMCYCINT_Pos) |

| #define | SCnSCB_ACTLR_DISMCYCINT_Pos 0 |

| #define | SCS_BASE (0xE000E000UL) |

| #define | SysTick ((SysTick_Type *) SysTick_BASE ) |

| #define | SysTick_BASE (SCS_BASE + 0x0010UL) |

| #define | SysTick_CALIB_NOREF_Msk (1UL << SysTick_CALIB_NOREF_Pos) |

| #define | SysTick_CALIB_NOREF_Pos 31 |

| #define | SysTick_CALIB_SKEW_Msk (1UL << SysTick_CALIB_SKEW_Pos) |

| #define | SysTick_CALIB_SKEW_Pos 30 |

| #define | SysTick_CALIB_TENMS_Msk (0xFFFFFFUL << SysTick_VAL_CURRENT_Pos) |

| #define | SysTick_CALIB_TENMS_Pos 0 |

| #define | SysTick_CTRL_CLKSOURCE_Msk (1UL << SysTick_CTRL_CLKSOURCE_Pos) |

| #define | SysTick_CTRL_CLKSOURCE_Pos 2 |

| #define | SysTick_CTRL_COUNTFLAG_Msk (1UL << SysTick_CTRL_COUNTFLAG_Pos) |

| #define | SysTick_CTRL_COUNTFLAG_Pos 16 |

| #define | SysTick_CTRL_ENABLE_Msk (1UL << SysTick_CTRL_ENABLE_Pos) |

| #define | SysTick_CTRL_ENABLE_Pos 0 |

| #define | SysTick_CTRL_TICKINT_Msk (1UL << SysTick_CTRL_TICKINT_Pos) |

| #define | SysTick_CTRL_TICKINT_Pos 1 |

| #define | SysTick_LOAD_RELOAD_Msk (0xFFFFFFUL << SysTick_LOAD_RELOAD_Pos) |

| #define | SysTick_LOAD_RELOAD_Pos 0 |

| #define | SysTick_VAL_CURRENT_Msk (0xFFFFFFUL << SysTick_VAL_CURRENT_Pos) |

| #define | SysTick_VAL_CURRENT_Pos 0 |

| #define | __SC000_CMSIS_VERSION_MAIN (0x03) |

| #define | __SC000_CMSIS_VERSION_SUB (0x01) |

| #define | __SC000_CMSIS_VERSION |

| #define | __CORTEX_SC (0) |

| #define | __FPU_USED 0 |

| __FPU_USED indicates whether an FPU is used or not. | |

| #define | __CORE_SC000_H_DEPENDANT |

| #define | __I volatile const |

| #define | __O volatile |

| #define | __IO volatile |

Функции | |

| __STATIC_INLINE void | NVIC_ClearPendingIRQ (IRQn_Type IRQn) |

| Clear Pending Interrupt. | |

| __STATIC_INLINE void | NVIC_DisableIRQ (IRQn_Type IRQn) |

| Disable External Interrupt. | |

| __STATIC_INLINE void | NVIC_EnableIRQ (IRQn_Type IRQn) |

| Enable External Interrupt. | |

| __STATIC_INLINE uint32_t | NVIC_GetPendingIRQ (IRQn_Type IRQn) |

| Get Pending Interrupt. | |

| __STATIC_INLINE uint32_t | NVIC_GetPriority (IRQn_Type IRQn) |

| Get Interrupt Priority. | |

| __STATIC_INLINE void | NVIC_SetPendingIRQ (IRQn_Type IRQn) |

| Set Pending Interrupt. | |

| __STATIC_INLINE void | NVIC_SetPriority (IRQn_Type IRQn, uint32_t priority) |

| Set Interrupt Priority. | |

| __STATIC_INLINE void | NVIC_SystemReset (void) |

| System Reset. | |

| __STATIC_INLINE uint32_t | SysTick_Config (uint32_t ticks) |

| System Tick Configuration. | |

CMSIS SC000 Core Peripheral Access Layer Header File.

См. определение в файле core_sc000.h

| #define __CORE_SC000_H_DEPENDANT |

См. определение в файле core_sc000.h строка 120

| #define __CORE_SC000_H_GENERIC |

См. определение в файле core_sc000.h строка 32

| #define __CORTEX_SC (0) |

Cortex secure core

См. определение в файле core_sc000.h строка 61

| #define __FPU_USED 0 |

__FPU_USED indicates whether an FPU is used or not.

This core does not support an FPU at all

См. определение в файле core_sc000.h строка 88

| #define __I volatile const |

Defines 'read only' permissions

См. определение в файле core_sc000.h строка 156

| #define __IO volatile |

Defines 'read / write' permissions

См. определение в файле core_sc000.h строка 159

| #define __O volatile |

Defines 'write only' permissions

См. определение в файле core_sc000.h строка 158

| #define __SC000_CMSIS_VERSION |

CMSIS HAL version number

См. определение в файле core_sc000.h строка 58

| #define __SC000_CMSIS_VERSION_MAIN (0x03) |

[31:16] CMSIS HAL main version

См. определение в файле core_sc000.h строка 56

| #define __SC000_CMSIS_VERSION_SUB (0x01) |

[15:0] CMSIS HAL sub version

См. определение в файле core_sc000.h строка 57