|

CMSIS2000

0.0.7

|

|

CMSIS2000

0.0.7

|

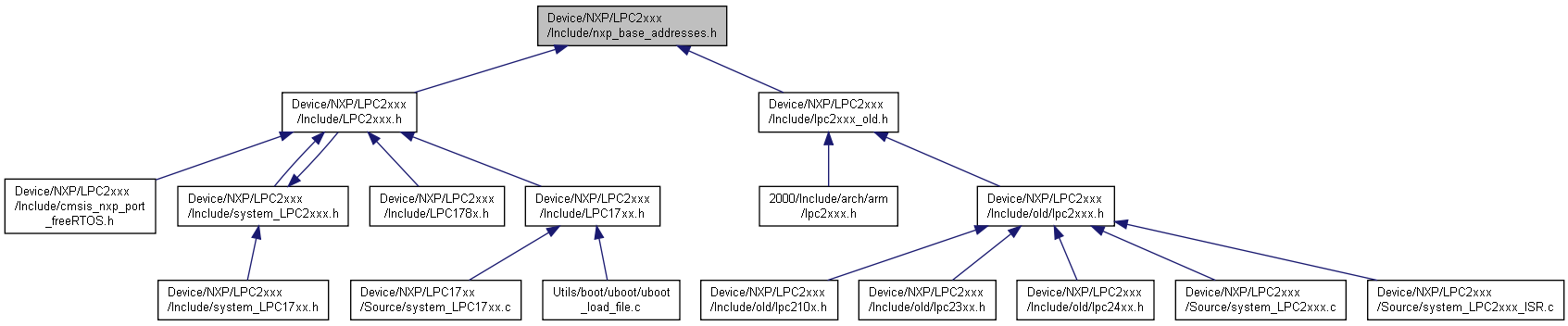

APB(ARM Peripheral Bus) peripheries base addresses. More...

Go to the source code of this file.

Macros | |

| #define | LPC_AD0_BASE 0xE0034000 |

| A/D Converter 0 (AD0) base address. | |

| #define | LPC_AHB_BASE (0xF0000000UL) |

| #define | LPC_AHBRAM0_BASE (0x7FE00000UL) /*Ethernet RAM (16 kB*/ |

| #define | LPC_AHBRAM1_BASE (0x7FD00000UL) /* USB RAM (16 kB)*/ |

| #define | LPC_APB0_BASE (0xE0000000UL) |

| #define | LPC_APB1_BASE LPC_APB0_BASE |

| #define | LPC_CAN1_BASE 0xE0044000 |

| #define | LPC_CAN2_BASE 0xE0048000 |

| #define | LPC_CAN_ACCEPT_BASE 0xE003C000 |

| CAN CONTROLLERS AND ACCEPTANCE FILTER base address. | |

| #define | LPC_CAN_CENTRAL_BASE 0xE0040000 |

| #define | LPC_DAC_BASE 0xE006C000 |

| D/A Converter base address. | |

| #define | LPC_DYNAMIC_MEM0_BASE 0xA0000000 |

| #define | LPC_DYNAMIC_MEM1_BASE 0xB0000000 |

| #define | LPC_DYNAMIC_MEM2_BASE 0xC0000000 |

| #define | LPC_DYNAMIC_MEM3_BASE 0xD0000000 |

| #define | LPC_EMC_BASE 0xFFE08000 |

| External Memory Controller (EMC) base address. | |

| #define | LPC_EMC_BASE 0xFFE08000 |

| External Memory Controller (EMC) base address. | |

| #define | LPC_FIO_BASE 0x3FFFC000 |

| Fast I/O setup base address. | |

| #define | LPC_FLASH_BASE (0x00000000UL) |

| #define | LPC_GPDMA_BASE 0xFFE04000 |

| General-purpose DMA Controller base address. | |

| #define | LPC_GPDMACH0_BASE 0xFFE04100 |

| General-purpose DMA Controller channel 0 base address. | |

| #define | LPC_GPDMACH1_BASE 0xFFE04120 |

| General-purpose DMA Controller channel 1 base address. | |

| #define | LPC_GPIO0_BASE (LPC_FIO_BASE + 0x00000) |

| #define | LPC_GPIO1_BASE (LPC_FIO_BASE + 0x00020) |

| #define | LPC_GPIO2_BASE (LPC_FIO_BASE + 0x00040) |

| #define | LPC_GPIO3_BASE (LPC_FIO_BASE + 0x00060) |

| #define | LPC_GPIO4_BASE (LPC_FIO_BASE + 0x00080) |

| #define | LPC_GPIO_BASE 0xE0028000 |

| General Purpose Input/Output (GPIO) | |

| #define | LPC_GPIOINT_BASE 0xE0028080 |

| #define | LPC_I2C0_BASE 0xE001C000 |

| I2C Interface 0 base address. | |

| #define | LPC_I2C1_BASE 0xE005C000 |

| I2C Interface 1 base address. | |

| #define | LPC_I2C2_BASE 0xE0080000 |

| I2C Interface 2 base address. | |

| #define | LPC_I2S_BASE 0xE0088000 |

| I2S Interface Controller (I2S) base address. | |

| #define | LPC_MAC_BASE 0xFFE00000 /* AHB Peripheral # 0 */ |

| Ethernet MAC (32 bit data bus) base address. | |

| #define | LPC_MCI_BASE 0xE008C000 |

| MultiMedia Card Interface(MCI) Controller base address. | |

| #define | LPC_PARTCFG_BASE 0x3FFF8000 |

| #define | LPC_PINSEL_BASE 0xE002C000 |

| Pin Connect Block base address. | |

| #define | LPC_PWM0_BASE 0xE0014000 |

| Pulse Width Modulator (PWM) base address. | |

| #define | LPC_PWM1_BASE 0xE0018000 |

| #define | LPC_RAM_BASE (0x40000000UL) |

| #define | LPC_RTC_BASE 0xE0024000 |

| Real Time Clock base address. | |

| #define | LPC_SC_BASE 0xE01FC000 |

| System Control Block(SCB) base address. | |

| #define | LPC_SPI0_BASE 0xE0020000 |

| SPI0 (Serial Peripheral Interface 0) base address. | |

| #define | LPC_SSP0_BASE 0xE0068000 |

| SSP0 Controller base address. | |

| #define | LPC_SSP1_BASE 0xE0030000 |

| SSP1 Controller base address. | |

| #define | LPC_STATIC_MEM0_BASE 0x80000000 |

| MPMC(EMC) registers, note: all the external memory controller(EMC) registers are for LPC24xx only. | |

| #define | LPC_STATIC_MEM1_BASE 0x81000000 |

| #define | LPC_STATIC_MEM2_BASE 0x82000000 |

| #define | LPC_STATIC_MEM3_BASE 0x83000000 |

| #define | LPC_TIM0_BASE 0xE0004000 |

| Timer 0 base address. | |

| #define | LPC_TIM1_BASE 0xE0008000 |

| Timer 1 base address. | |

| #define | LPC_TIM2_BASE 0xE0070000 |

| Timer 2 base address. | |

| #define | LPC_TIM3_BASE 0xE0074000 |

| Timer 3 base address. | |

| #define | LPC_UART0_BASE 0xE000C000 |

| Universal Asynchronous Receiver Transmitter 0 (UART0) base address. | |

| #define | LPC_UART1_BASE 0xE0010000 |

| Universal Asynchronous Receiver Transmitter 1 (UART1) base address. | |

| #define | LPC_UART2_BASE 0xE0078000 |

| Universal Asynchronous Receiver Transmitter 2 (UART2) base address. | |

| #define | LPC_UART3_BASE 0xE007C000 |

| Universal Asynchronous Receiver Transmitter 3 (UART3) base address. | |

| #define | LPC_USB_BASE 0xFFE0C200 |

| #define | LPC_USB_INT_BASE 0xE01FC1C0 |

| USB Controller base address. | |

| #define | LPC_USBHC_BASE 0xFFE0C000 /* for LPC24xx only */ |

| USB Host Controller and OTG registers base address. | |

| #define | LPC_USBOTG_BASE 0xFFE0C100 |

| USB OTG Controller base address. | |

| #define | LPC_USBOTG_CLK_BASE 0xFFE0CFF0 |

| #define | LPC_USBOTG_I2C_BASE 0xFFE0C300 |

| #define | LPC_WDG_BASE 0xE0000000 |

| Watchdog base address. | |

| #define | LPC_WDT_BASE LPC_WDG_BASE |

| #define | VIC_BASE 0xFFFFF000 |

| ————-SYSTEM ——————————————————– | |

APB(ARM Peripheral Bus) peripheries base addresses.

Definition in file nxp_base_addresses.h.