|

CMSIS2000

0.0.7

|

|

CMSIS2000

0.0.7

|

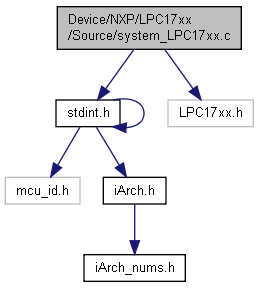

CMSIS Cortex-M3 Device Peripheral Access Layer Source File for the NXP LPC17xx Device Series. More...

Go to the source code of this file.

Macros | |

| #define | __CCLK_DIV (((CCLKCFG_Val ) & 0x00FF) + 1) |

| #define | __CORE_CLK (__FCCO(OSC_CLK) / __CCLK_DIV) |

| #define | __FCCO(__F_IN) ((2 * __M * __F_IN) / __N) |

| #define | __M (((PLL0CFG_Val ) & 0x7FFF) + 1) |

| #define | __N (((PLL0CFG_Val >> 16) & 0x00FF) + 1) |

| #define | CCLKCFG_Val 0x00000003 |

| #define | CHECK_RANGE(val, min, max) ((val < min) || (val > max)) |

| #define | CHECK_RSVD(val, mask) (val & mask) |

| #define | CLKOUTCFG_Val 0x00000000 |

| #define | CLKSRCSEL_Val 0x00000001 |

| #define | CLOCK_SETUP 1 |

| #define | FLASH_SETUP 1 |

| #define | FLASHCFG_Val 0x0000303A |

| #define | IRC_OSC ( 4000000UL) /* Internal RC oscillator frequency */ |

| #define | OSC_CLK ( XTAL_HZ) /* Main oscillator frequency */ |

| #define | PCLKSEL0_Val 0x00000000 |

| #define | PCLKSEL1_Val 0x00000000 |

| #define | PCONP_Val 0x042887DE |

| #define | PLL0_SETUP 1 |

| #define | PLL0CFG_Val 0x00050063 |

| #define | PLL1_SETUP 1 |

| #define | PLL1CFG_Val 0x00000023 |

| #define | RTC_CLK ( 32768UL) /* RTC oscillator frequency */ |

| #define | SCS_Val 0x00000020 |

| #define | USBCLKCFG_Val 0x00000000 |

| #define | XTAL_HZ (12000000UL) /* Oscillator frequency */ |

Functions | |

| void | SystemCoreClockUpdate (void) |

| Update SystemCoreClock variable. | |

| void | SystemInit (void) |

| Initialize the system. | |

Variables | |

| uint32_t | __isr_vector |

| uint32_t | SystemCoreClock = __CORE_CLK |

CMSIS Cortex-M3 Device Peripheral Access Layer Source File for the NXP LPC17xx Device Series.

Definition in file system_LPC17xx.c.