|

CMSIS2000

0.0.7

|

|

CMSIS2000

0.0.7

|

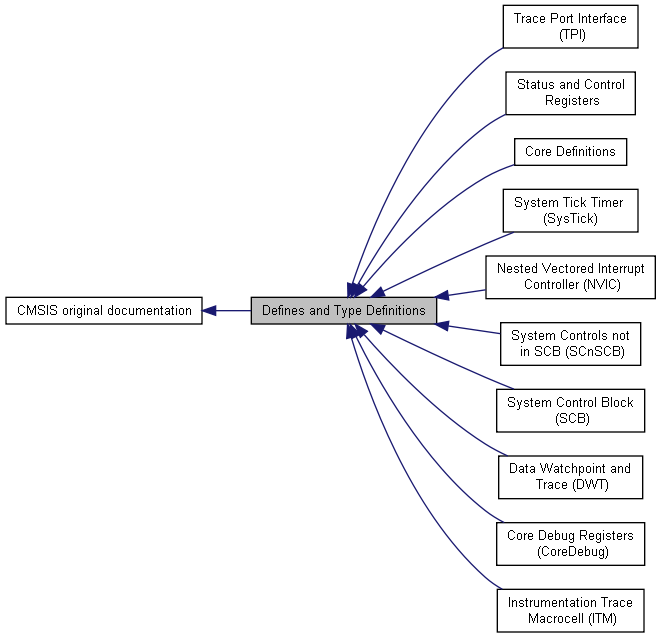

Type definitions and defines for Cortex-M processor based devices. More...

|

Modules | |

| Status and Control Registers | |

| Core Register type definitions. | |

| Nested Vectored Interrupt Controller (NVIC) | |

| Type definitions for the NVIC Registers. | |

| System Control Block (SCB) | |

| Type definitions for the System Control Block Registers. | |

| System Tick Timer (SysTick) | |

| Type definitions for the System Timer Registers. | |

| Core Debug Registers (CoreDebug) | |

| Cortex-M0 Core Debug Registers (DCB registers, SHCSR, and DFSR) are only accessible over DAP and not via processor. | |

| Core Definitions | |

| Definitions for base addresses, unions, and structures. | |

| System Controls not in SCB (SCnSCB) | |

| Type definitions for the System Control and ID Register not in the SCB. | |

| Instrumentation Trace Macrocell (ITM) | |

| Type definitions for the Instrumentation Trace Macrocell (ITM) | |

| Data Watchpoint and Trace (DWT) | |

| Type definitions for the Data Watchpoint and Trace (DWT) | |

| Trace Port Interface (TPI) | |

| Type definitions for the Trace Port Interface (TPI) | |

Type definitions and defines for Cortex-M processor based devices.